# Printed Wiring Board Industry and Use Cluster Profile

Design for the Environment Program

Economics, Exposure and Technology Division

Office of Pollution Prevention and Toxics

U.S. Environmental Protection Agency

Washington, DC 20460

This document was produced under grant # X 823856-01-0 from EPA's Environmental Technology Initiative program.

#### ACKNOWLEDGMENTS

This report was prepared by Microelectronics and Computer Technology Corporation and The Institute for Interconnecting and Packaging Electronic Circuits as part of a multi-stakeholder, collaborative, Design for the Environment project. The EPA Project Officers were Kathy Hart and Debbie Boger of the Design for the Environment Staff of the Office of Pollution Prevention and Toxics. The report was constructed by Christopher Rhodes of the IPC and Greg Pitts of MCC, with valuable assistance in the preparation and review provided by: George Cushnie and Mark Eelman of CAI, Inc.; Steve Bold of Continental Circuits; Gary Roper of HR Industries; and Fritz Fehrer and Ted Smith of the Silicon Valley Toxics Coalition. Acknowledgment is also given to the members of the project Core Group, not mentioned above, who provided guidance and feedback throughout the preparation of the report, including: Michael Kerr of Circuit Center; John Lott of E.I. DuPont de Nemours; and Lori Kincaid of the University of Tennessee. Thanks also to Star Summerfield of the IPC and Jana Hellier of MCC for incorporating comments, editing, and formatting the report.

# **Table of Contents**

| EXE  | CUT                                     | TIVE SUMMARYE                                                                                                                                                                                                                                                                                                                                                                                               | S-1                                                                |

|------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| PAR  | T O                                     | NE: PWB INDUSTRY PROFILE                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| I.   | INTI<br>A.<br>B.<br>C.                  | RODUCTION AND OVERVIEW What is a PWB? Independent vs. Captive Production General Nature of Industry.                                                                                                                                                                                                                                                                                                        | 1-1<br>1-1                                                         |

| II.  | COI<br>A.<br>B.                         | MPANIES AND FACILITIES                                                                                                                                                                                                                                                                                                                                                                                      | 1-3                                                                |

| III. | FINA<br>A.<br>B.                        | ANCIAL ANALYSIS OF INDUSTRY Profitability Operating and Financial Ratios                                                                                                                                                                                                                                                                                                                                    | 1-5<br>1-5<br>1-5                                                  |

| IV.  | MA<br>A.<br>B.<br>C.<br>D.<br>E.        | RKET ANALYSIS OF INDUSTRY                                                                                                                                                                                                                                                                                                                                                                                   | 1-6<br>1-6<br>-10<br>-10                                           |

| V.   | TEC<br>A.<br>B.<br>C.<br>D.<br>E.<br>F. | HNOLOGY TRENDS ANALYSIS OF INDUSTRY                                                                                                                                                                                                                                                                                                                                                                         | -13<br>-14<br>-15<br>-15<br>-16                                    |

| PAF  | RT TV                                   | WO: PWB USE CLUSTER PROFILE                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| I.   | OVE<br>A.<br>B.<br>C.                   | Introduction Use Cluster Profile. Overview of PWB Types and Manufacturing Methods  1. Single-sided Manufacturing Overview. 2. Double-sided Manufacturing Overview. 3. Multilayer Manufacturing Overview. 4. Flexible PWB Manufacturing Overview. 5. Subtractive Overview. 6. Additive Overview. 7. Additive Metallization Techniques. a. Solid Systems. b. Screen Printing. c. Liquid. d. Sequential Build. | 2-1<br>2-1<br>2-2<br>2-2<br>2-4<br>2-4<br>2-5<br>2-6<br>2-7<br>2-7 |

# Table of Contents (continued)

## PART TWO: USE CLUSTER PROFILE OF THE PWB INDUSTRY (continued)

| II. | CLI | USTE     | ERS FOR RIGID MULTILAYER PWB MANUFACTURING     | 2-10 |

|-----|-----|----------|------------------------------------------------|------|

|     | A.  | Dat      | ta Acquisition and Computer-aided Design (CAD) | 2-10 |

|     | В.  | Inne     | er Layer Image Transfer                        | 2-11 |

|     |     | 1.       | Overview                                       |      |

|     |     | 2.       | Conventional Print-and-Etch                    | 2-11 |

|     |     |          | a. Photo-tool Creation                         |      |

|     |     |          | b. Material Preparation                        |      |

|     |     |          | c. Imaging                                     | 2-14 |

|     |     |          | d. Etching                                     | 2-15 |

|     |     |          | e. Resist Stripping                            | 2-16 |

|     |     |          | f. Oxide                                       |      |

|     |     | 3.       | Image Transfer Options                         | 2-16 |

|     |     | ٥.       | n Direct Imagina                               | 2 16 |

|     |     |          | a. Direct Imagingb. Pre-treated Materials      | 2 17 |

|     | ~   | Υ        |                                                |      |

|     | C.  |          | mination                                       |      |

|     | D.  |          |                                                |      |

|     |     | 1.       | Överview                                       | 2-18 |

|     |     | 2.       | Conventional CNC Drilling                      | 2-19 |

|     |     |          | a. Introduction                                |      |

|     |     |          | b. Entry Material                              | 2-19 |

|     |     |          | c. Back-up Material                            | 2-19 |

|     |     |          | d. Drill Bits and Process                      |      |

|     |     | 3.       | Laser Ablation                                 |      |

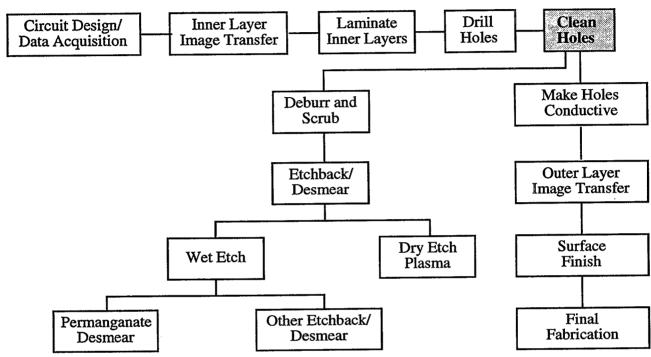

|     | E.  | Hol      | le Cleaning                                    |      |

|     |     | 1.       | Overview                                       | 2-21 |

|     |     | 2.       | Wet Chemical Desmear and Etchback              | 2-22 |

|     |     |          | a. Wet Chemical Methods                        | 2-22 |

|     |     |          | b. Plasma Etchback                             | 2-23 |

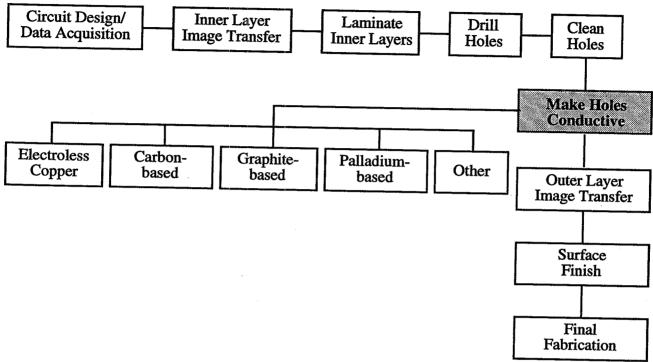

|     | F.  | Mal      | king Holes Conductive                          |      |

|     |     | 1.       | Överview                                       | 2-24 |

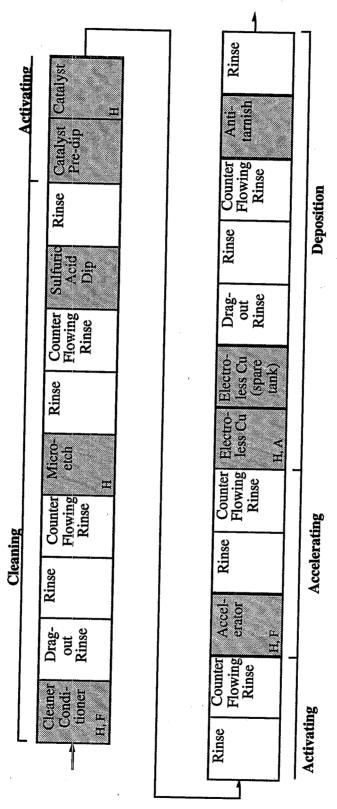

|     |     | 2.       | Electroless Copper                             | 2-26 |

|     |     | ~.       | a. Cleaning                                    | 2-26 |

|     |     |          | b. Activation and Acceleration                 | 2-26 |

|     |     |          | c. Copper Deposition                           | 2-26 |

|     |     |          | d. Process Waste Streams                       | 2-28 |

|     |     | 3.       | Carbon-based Alternatives                      |      |

|     |     | 3.<br>4. | Graphite-based Alternative.                    |      |

|     |     | 4.       | Graphite-Dasco Alternative                     | 2 20 |

|     |     |          | a. Cleaning and Conditioningb. Graphite        | 2 20 |

|     |     |          |                                                |      |

|     |     |          | c. Micro-etch                                  | 2.20 |

|     |     |          | d. Anti-tarnish                                | 2-30 |

|     |     |          | e. Process Waste Streams                       |      |

|     |     | 5.       | Palladium-based Alternatives                   | 2-30 |

|     |     |          | a. Cleaner/Conditioner                         | 2-30 |

|     |     |          | b. Micro-etch                                  | 2-31 |

|     |     |          | c. Drying                                      | 2-31 |

|     |     |          | d. Process Waste Streams                       | 2-31 |

# Table of Contents (continued)

# PART TWO: PWB USE CLUSTER PROFILE (continued)

| II.  | CLU  | JSTERS FOR RIGID MULTILAYER PWB MANUFACTURING (continued)               | i    |

|------|------|-------------------------------------------------------------------------|------|

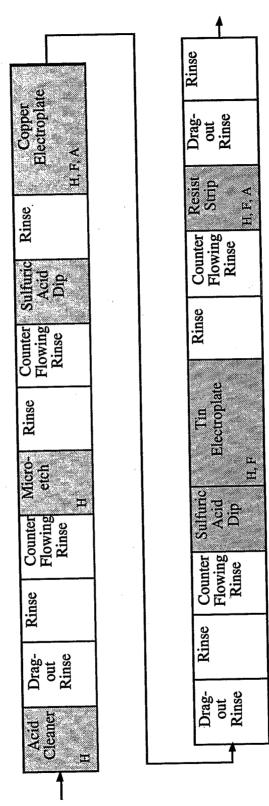

|      | G.   | Outer Layer Image Transfer                                              | 2-31 |

|      |      | 1. Overview                                                             | 2-31 |

|      |      | <ol> <li>Overview</li></ol>                                             | 2-33 |

|      |      | a. Imaging                                                              | 2-33 |

|      |      | b. Pattern Plating Copper                                               | 2-33 |

|      |      | c. Pattern Plating Etch-resist                                          | 2-35 |

|      |      | d. Photoresist Stripping                                                | 2-36 |

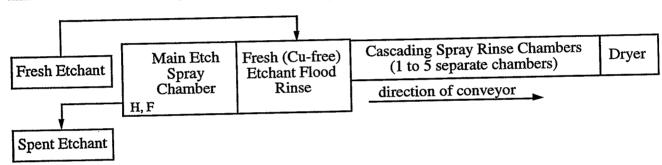

|      |      | e. Outer Layer Etching                                                  | 2-36 |

|      |      | f. Tin and Tin-Lead Stripping                                           | 2-36 |

|      |      | 3. Panel-Plate, Print, and Etch ("Tent-and-Etch")                       | 2-36 |

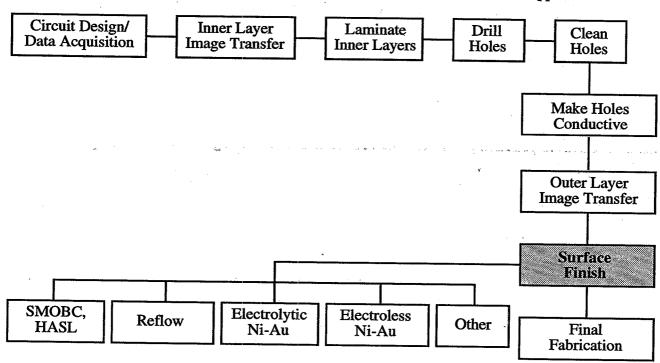

|      | Η.   | Surface Finish                                                          | 2-37 |

|      |      | 1. Overview                                                             | 2-37 |

|      |      | 2. Solder Mask Over Bare Copper (SMOBC), Hot Air Solder Level (HASL)    | 2-38 |

|      |      | a. Solder Mask                                                          | 2-38 |

|      |      | a. Solder Maskb. Hot Air Solder Level (HASL)                            | 2-38 |

|      |      | 3. Reflowed Tin-Lead                                                    | 2-30 |

|      |      | 4. Nickel/Gold                                                          | 2-39 |

|      |      | a. Hard Gold                                                            |      |

|      |      | b. Soft Electrolytic Gold                                               | 2-39 |

|      |      | b. Soft Electrolytic Gold                                               | 2-39 |

|      | I.   | Final Fabrication                                                       | 2-40 |

|      | _,   |                                                                         |      |

| III. | SU   | PPORT OPERATIONS                                                        | 2-41 |

| -    | A.   | Waste Treatment                                                         | 2-41 |

|      | В.   | Waste Streams                                                           | 2-41 |

|      |      | 1. Solvents                                                             |      |

|      |      | 2. Process Baths                                                        |      |

|      |      |                                                                         |      |

| IV.  | SEL  | ECTING A USE-CLUSTER FOR A DfE PROJECT                                  | 2-43 |

|      | A.   | Cleaner Technology Substitute Assessment                                | 2-43 |

|      | В.   | Use Cluster Scoring System                                              | 2-43 |

|      | C.   | Use Cluster Scoring System Use Cluster Selection in the DfE PWB Project | 2-43 |

|      | D.   | Future Design for Environment Projects                                  | 2-44 |

|      |      |                                                                         |      |

| REF  | ERE  | ENCES                                                                   | R-1  |

|      |      |                                                                         |      |

|      |      |                                                                         |      |

| API  | PENI | DIX                                                                     |      |

|      |      |                                                                         |      |

| Α.   | Glos | ssary of Terms                                                          | A-1  |

## List of Tables

| 1-1 | Distribution of PWB Manufacturing Facilities, 1994                      | 1-3  |

|-----|-------------------------------------------------------------------------|------|

| 1-2 | U.S. Independent PWB Manufacturers: Number and Size of Company by Sales | 1-4  |

| 1-3 | Quantity and Value of Domestic PWB Production                           | 1-8  |

| 1-4 | Domestic Rigid PWB and Laminate Production by Type of Substrate Used    | 1-12 |

| 2-1 | Lasers Available for Via Formation in PWB Fabrication                   | 2-20 |

| 2-2 | Plasma Etchback Parameters                                              | 2-24 |

# List of Figures

| 1-1          | U.S. Independent PWB Manufacturers: Market Share by Size of Company1-4                                                                                                |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2          | U.S. Dollar Denominated Share of World Rigid PWB Market for Selected Countries/Regions1-6                                                                             |

| 1-3          | U.S. Dollar Denominated Production of World Rigid PWB Market by Type of Substrate 1-7                                                                                 |

| 1-4          | Historical World Market Share for Rigid and Flexible Circuits 1-7                                                                                                     |

| 1-5          | Comparison: Multilayers (including high-performance multilayers) vs. All Other Rigid PWBs (excluding flex)                                                            |

| 1-6          | Historic Trends of Make vs. Buy for PWB Production in the U.S1-9                                                                                                      |

| 1-7          | Market for PWBs in the United States in 19931-11                                                                                                                      |

| 1-8          | Sales of Various Process Consumables for Rigid Boards in 19931-12                                                                                                     |

| 1-9          | Historical Trends for Layer Count in Multilayer PWBs                                                                                                                  |

| 1-10         | Historical Trends on Surface Mount Applications in PWB Production1-14                                                                                                 |

| 1-11         | Use of Fine-pitch Technology1-15                                                                                                                                      |

| 1-12         | Density of PWB Production Based on Dollar Value of Production: OEM vs. Independents                                                                                   |

| 1-13         | Percent of Production for Various Hole Sizes Based on Dollar Value of Production for 19931-17                                                                         |

| 1-14         | Percent Usage of ≤0.019" Holes from 1985 through 1993 Based on Dollar Value of Production                                                                             |

| 1-15         | Historical Trends in PWB Surface Finish Techniques Based on Dollar Value of Production                                                                                |

| 1-16         | Historical Trends in PWB Protective Coating Techniques1-18                                                                                                            |

| 1-17         | Worldwide IC Packaging Methods1-19                                                                                                                                    |

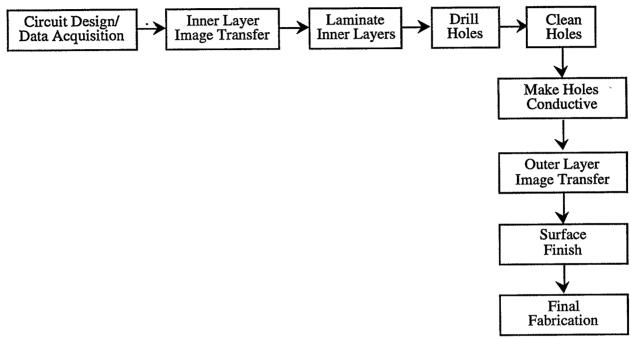

| 2-1          | The Basic Manufacturing Flow for the Fabrication of Rigid Multilayer PWBs2-3                                                                                          |

| <b>2-2</b> . | The Simplified Subtractive Process for Manufacturing Inner Layers of Rigid Multilayers, and a Cross-Section of Two Inner Layer Cores within a Multilayer Structure2-5 |

| 2-3          | The Simplified Full-Build Additive Process for Manufacturing Inner Layers of Rigid Multilayers, and a Cross-Section of a Multilayer Structure                         |

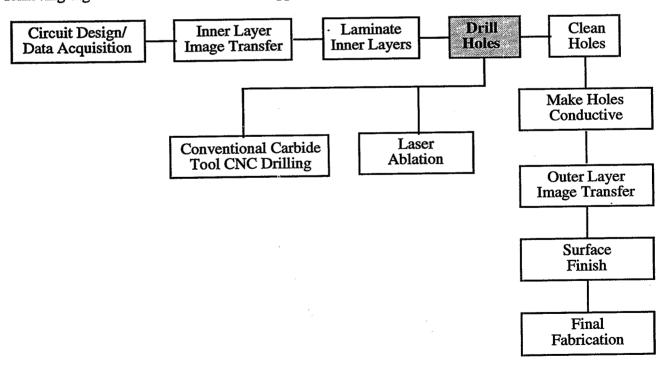

| 2-4  | Typical Process Flow for PWB Manufacture                           | 2-10 |

|------|--------------------------------------------------------------------|------|

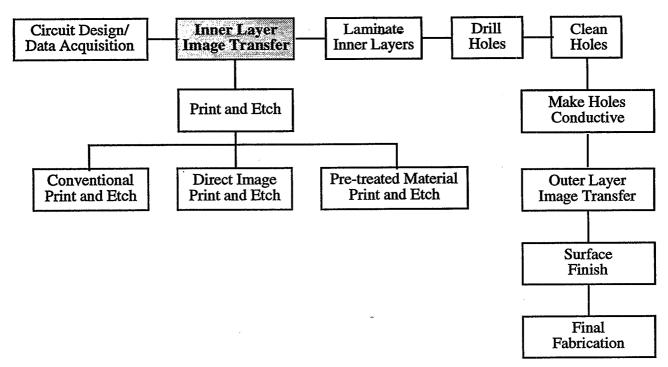

| 2-5  | Inner Layer Image Transfer Use Cluster                             | 2-12 |

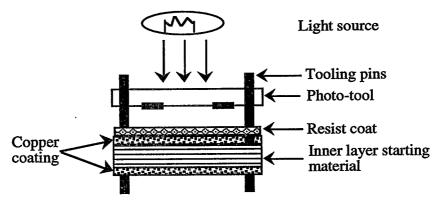

| 2-6  | Schematic Drawing of an Exposure Tool for Inner Layers             | 2-12 |

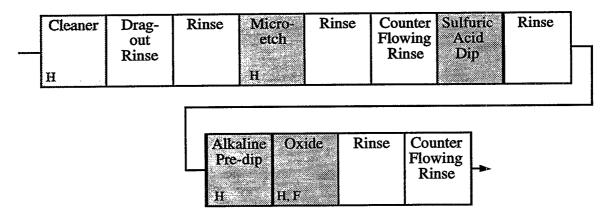

| 2-7  | Typical Oxide Process Line                                         | 2-16 |

| 2-8  | Drill Holes Use Cluster                                            | 2-18 |

| 2-9  | Clean Holes Use Cluster                                            | 2-22 |

| 2-10 | Typical Desmear Process Line                                       | 2-23 |

| 2-11 | Make Holes Conductive Use Cluster                                  | 2-25 |

| 2-12 | Typical Electroless Copper Plating Line                            | 2-27 |

| 2-13 | Outer Layer Image Transfer Use Cluster                             | 2-32 |

| 2-14 | Typical Pattern Plate, Etch-resist, Photoresist Strip Process Line | 2-34 |

| 2-15 | Typical Ammoniacal Etch Process                                    | 2-36 |

| 2-16 | Surface Finish Use Cluster                                         | 2-37 |

CONTRACTOR AND AND ARTHUR TRIVERS OF THE PROPERTY OF THE PROPERTY AND AND ASSESSED TO A CONTRACT OF THE PROPERTY AND ASSESSED TO A CONTRACT OF THE PROPERTY OF

TO A COLOR OF A COLOR OF A COLOR OF A COLOR OF A SECTION AND A SECTION ASSESSMENT AND A COLOR OF A

#### **EXECUTIVE SUMMARY**

This report presents a profile of the printed wiring board (PWB) industry, and defines and describes the typical manufacturing steps or "use clusters" in the manufacture of multilayer rigid PWBs.

#### INTRODUCTION

PWBs serve to interconnect the devices and components in the vast majority of electronic products. Without this critical component, most electronic products either could not function or would be significantly more expensive if constructed with other interconnect technologies. PWBs play a crucial role in the advancement of electronic packaging and interconnections because improvements in PWBs reduce the size and cost of electronic devices while boosting performance. Progress in PWB technology and manufacturing drives U.S. competitiveness in both existing products and new technologies. The U.S. Department of Defense (DoD), the U.S. Department of Commerce (DoC), the Japanese Ministry of International Trade and Industry (MITI), and the European Community (EC) all include electronic systems and components on their critical technology lists.

#### **BACKGROUND**

A March 1993 report published by MCC (the Microelectronics and Computer Technology Corporation) entitled, <u>Environmental Consciousness</u>: A <u>Strategic Competitiveness Issue for the Electronics and Computer Industry</u>, identified key environmental technology needs in electronics systems manufacturing. The study concluded that effective collaboration between government, industry, academia, and the public is vital for developing and implementing environmentally conscious products and processes. Industry and government programs in environmental technology should encourage such collaboration and focus on specific pilot projects.

The study effort stimulated a collaborative effort to develop a roadmap for the electronics industry. The final roadmap document, released in December of 1994, was produced through a collaborative process that collectively involved more than 100 organizations, including the Advanced Research Projects Agency (ARPA), DoE and the Environmental Protection Agency (EPA), and several prominent trade associations. The Institute for Interconnecting and Packaging Electronic Circuits (IPC) was instrumental in developing the information on PWBs through its Environment, Health, and Safety Committee. The EPA Design for the Environment PWB Project was stimulated in part by both of these activities.

#### DESIGN FOR THE ENVIRONMENT PROJECT

This profile report was prepared in support of the U.S. EPA Design for the Environment PWB Project. The Project is a cooperative effort between the EPA, IPC, MCC, industry, research institutions, and public interest stakeholders to identify and assess environmentally safer substitute materials, processes, and technologies for the PWB industry. This report—a profile of the industry (Part 1) and description of the major industry processes (Part 2)—is one step in the overall assessment. The information contained in this report contributes to the selection of specific materials, processes, and technologies to be investigated further.

#### PART 1: INDUSTRY PROFILE

The total world market for all PWBs is approximately \$21 billion, of which U.S. production accounts for about one quarter (>\$5 billion). U.S. domination of this world market eroded from 1980 to

1990, but has come back slightly in recent years. However, like a commodity industry, the PWB industry is characterized by highly competitive global sourcing with very low profit margins.

There are approximately 700 to 750 independent PWB manufacturing facilities in the U.S. In addition, there are approximately 70 captive printed wiring board facilities. The states with the highest number of PWB manufacturing facilities are California, Minnesota, Texas, Illinois, Massachusetts, and Arizona. However, there are PWB manufacturing facilities in virtually all 50 states and territories. In sheer numbers, the vast majority of PWB manufacturers are small to medium enterprises with annual sales under \$10 million. In the U.S., the majority of PWBs (>75%) are produced by independent manufacturers. Many original equipment manufacturers (OEMs) have shut down their PWB operations and now buy their PWBs from independent manufacturers.

Since 1980, rigid multilayer PWBs have grown to dominate the domestic production value of all PWBs. Rigid multilayer boards now account for approximately 66% of the domestic market. One-quarter of the market is double-sided rigid boards, and the remainder are single-sided and flexible circuits. The market for multilayer boards has grown from approximately \$700 million in 1980, to almost \$3.4 billion in 1993. The PWB industry directly employs approximately 75,000 people. Of this number, about 68% of employment is concentrated in production jobs—the highest ratio of production jobs for U.S. electronic manufacturing.

IPC estimates that a minimum of 2% of PWB revenues in 1991 went to pay for pollution controls. In comparison, the average net profit for the PWB industry in 1991 was about 2.2% of sales. The cost of waste treatment (estimated at over \$140 million in 1990 for major merchant PWB manufacturers) and the additional regulatory burdens of recordkeeping, manifesting, and inventory reporting constitute a significant cost to the PWB manufacturers in this country. The fundamental processes, however, have remained the same and many pollution prevention efforts have reached their cost-effective limits. Part 2 of this document will describe the PWB manufacturing process and identify alternative technologies that may be evaluated in a design for the environment effort, thereby decreasing cost and environmental impact simultaneously.

#### PART 2: USE CLUSTER PROFILE

PWB manufacturing is a highly technical, complicated operation requiring large equipment investments and over fifty processes. The manufacturing processes described in Part 2 are organized and described in "use clusters." A use cluster is a set of chemicals, processes, and technologies that can substitute for one another to perform a specific function. A use cluster profile of the industry, therefore, describes alternate chemicals, processes, or technologies that may be used to complete each step or function in the entire PWB manufacturing process.

This PWB use-cluster profile describes the fabrication processes for the largest product segment of the industry, the rigid multilayer PWB. The use cluster profile is intended to aid in the selection of a use cluster for assessment in a DfE project. The profile identifies different processes in the PWB industry (e.g., laminating, making holes conductive) and steps within those processes (e.g., imaging, etching, plating). The process steps are described in flow chart form with a description of each step. Next, the chemicals, processes, and technologies used in each step are briefly described. The profile may also mention commonly accepted alternatives to these practices and areas that are recognized to have especially high environmental impacts. Information on the risk and releases of these materials can then be investigated to target areas for further work but is not within the scope of this report.

# PART ONE: PWB INDUSTRY PROFILE

,

The same of the sa

A COMPANY OF THE STATE OF THE S

#### I. INTRODUCTION AND OVERVIEW

This industry profile refers to the printed wiring board (PWB) industry, SIC 3672.

#### A. What is a PWB?

A printed wiring board (PWB) is the foundation—both literally and figuratively—for virtually all electronics in the world. It is the platform upon which electronic components such as integrated circuit chips and capacitors are mounted. The PWB, or printed circuit board (PCB) provides both the physical structure for mounting and holding electronic components as well as the electrical interconnection between components. A PWB consists of a non-conducting substrate (typically fiberglass with epoxy resin) upon which a conductive pattern or circuitry is formed. Copper is the most prevalent conductor, although nickel, silver, tin, tin-lead, and gold may also be used as etch-resists or top-level metal. There are three types of PWBs: single-sided, double-sided, and multilayer. Single-sided boards have a conductive pattern on one side only, double-sided boards have conductive patterns on both faces, and multilayer boards consist of alternating layers of conductor and insulating material bonded together. The conductive layers are connected by plated through-holes, which are also used to mount and electrically connect components. PWBs may also be either rigid, flexible, or a combination of the two (rigid-flex).

When the electronic components have been mounted on the PWB, the combination of PWB and components is an electronic assembly, also called a printed wiring assembly (PWA). This assembly is the basic building block for all larger electronic systems, from toys to toasters to telecommunications.

These electronic systems, in turn, support every other critical technology in the United States. To quote the Council on Competitiveness from their 1991 <u>Gaining New Ground</u> report, "Electronic components are playing an especially important role in driving improvements in information and communication technologies, which in turn are enabling advances in all manufacturing and service industries."

PWBs play a crucial role in these improvements because advances in electronic packaging and interconnections reduce the size and cost of electronic devices while boosting performance. Progress in PWB technology and manufacturing drives U.S. competitiveness in both existing products and new technologies. The U.S. Department of Defense, the U.S. Department of Commerce, the Japanese Ministry of International Trade and Industry, and the European Community all include electronic systems and components on their critical technology lists.

Electronics drive productivity in almost every industry—one electronics job determines the competitive strength of seven jobs in other industries. Electronics are critical in medical systems, defense technologies, information processing, intelligent manufacturing, propulsion, and materials processing. In addition, a number of new, emerging industries depend on advancing the technical capability of the PWB industry. These include artificial intelligence, biotechnology, digital imaging technology, high-density data storage, high-performance computing, medical devices and diagnostics, opto-electronics, and more. U.S. competitiveness in these new technologies will depend upon advanced PWB technology and manufacturing capability in the United States.

#### B. <u>Independent vs. Captive Production</u>

PWBs are produced by two types of manufacturers: independent and captive. An independent or merchant manufacturer produces PWBs for sale on the open market, to be used in electronic products such as TVs, computers, and so forth. Independent PWB manufacturers are thus competing

with each other in a global market to secure orders or contracts from customers. Typically, independent PWB manufacturers bid on their ability to make a product as specified by the customer; the PWBs or electronic interconnection products are almost always custom designed.

A captive manufacturer is also known as an Original Equipment Manufacturer or OEM. These companies manufacture PWBs for use internally in their own electronic products. Texas Instruments and AT&T are examples of OEMs. Some OEMs, such as IBM, which in the past have been exclusively captive manufacturers, have recently entered the merchant market as well.

In the United States, the majority of PWBs are produced by independent manufacturers. Many OEMs have shut down their PWB operations and now buy their PWBs from independent manufacturers. Unfortunately, as OEMs shut down their PWB manufacturing, they also discontinue research and development on new PWB manufacturing technology, processes, and materials. Because the average independent PWB manufacturer is orders-of-magnitude smaller than most OEMs, the independent PWB manufacturer lacks sufficient resources to conduct research on any scale approaching what the OEMs used to accomplish. Thus, PWB technology development in the United States has slowed down considerably.

#### C. General Nature of Industry

PWB manufacturing is a highly technical, complicated operation requiring large equipment investments and over fifty process steps. Because PWBs are designed for individual, specific applications, the PWB manufacturing industry is not considered a commodity industry. However, like a commodity industry, the PWB industry is characterized by highly competitive global sourcing with very low profit margins. Designs for specific PWBs can be transmitted electronically virtually anywhere in the world for fabrication.

In the United States, unlike some other areas of the world, the PWB industry has made substantial investments in pollution prevention and control, and is continuing to spend an average of 2.1% and as much as five percent of sales on regulatory compliance and pollution prevention. These investments have paid off with significant pollution prevention successes. For example, the Institute for Interconnecting and Packaging Electronic Circuits (IPC) and several IPC members won EPA Stratospheric Ozone Protection Awards for research on eliminating ozone-depleting substances from PWB manufacturing and assembly. Several IPC members have also won EPA 33/50 Pollution Prevention Awards for their aggressive work on preventing pollution, and many IPC members have won state or local awards for their proactive pollution reduction efforts.

#### II. COMPANIES AND FACILITIES

#### A. Number of Companies and Facilities

There are approximately 700 to 750 independent PWB manufacturing facilities in the U.S. In addition, there are approximately 70 captive printed wiring board facilities. The geographic distribution is shown in Table 1-1. The states with the highest PWB manufacturing are California, Minnesota, Texas, Illinois, Massachusetts, and Arizona. However, there are PWB manufacturing facilities in virtually all 50 states and territories.

| Region Description |                        | # of PWB Facilities |             |

|--------------------|------------------------|---------------------|-------------|

| Area               | States                 | Captive             | Independent |

| New England        | VT, NH, MA, CT, ME, RI | 9                   | 65          |

| Mid-Atlantic       | PA, NY, NJ             | 6                   | 68          |

| South Atlantic     | VA, WV, MD, DE, NC, SC | 6                   | 26          |

| Southeast          | TN, MS, AL, GA, FL, PR | 7                   | 49          |

| South Central      | TX, OK, AR, LA         | 6                   | 45          |

| Mid-Central        | IL, KS, MO, NE         | 4                   | 53          |

| North Central      | MT, ND, SD, MN, IA, WI | 8                   | 62          |

| East Central       | MI, IN, OH, KY         | 5                   | 48          |

| Mountain States    | WY, CO, UT, NV, AZ, NM | 7                   | 43          |

| Northwest          | OR, WA, AK, HI         | 4                   | 21          |

| No. California     |                        | 0                   | 85          |

| So. California     |                        | 6                   | 134         |

| Canada             | AB, MB, ON, QU, BC, SA | 2                   | 48          |

|                    | Total                  | 70                  | 747         |

Source: Kirk-Miller Associates, 1994.

Table 1-1. Distribution of PWB Manufacturing Facilities, 1994.

#### B. Size of Companies

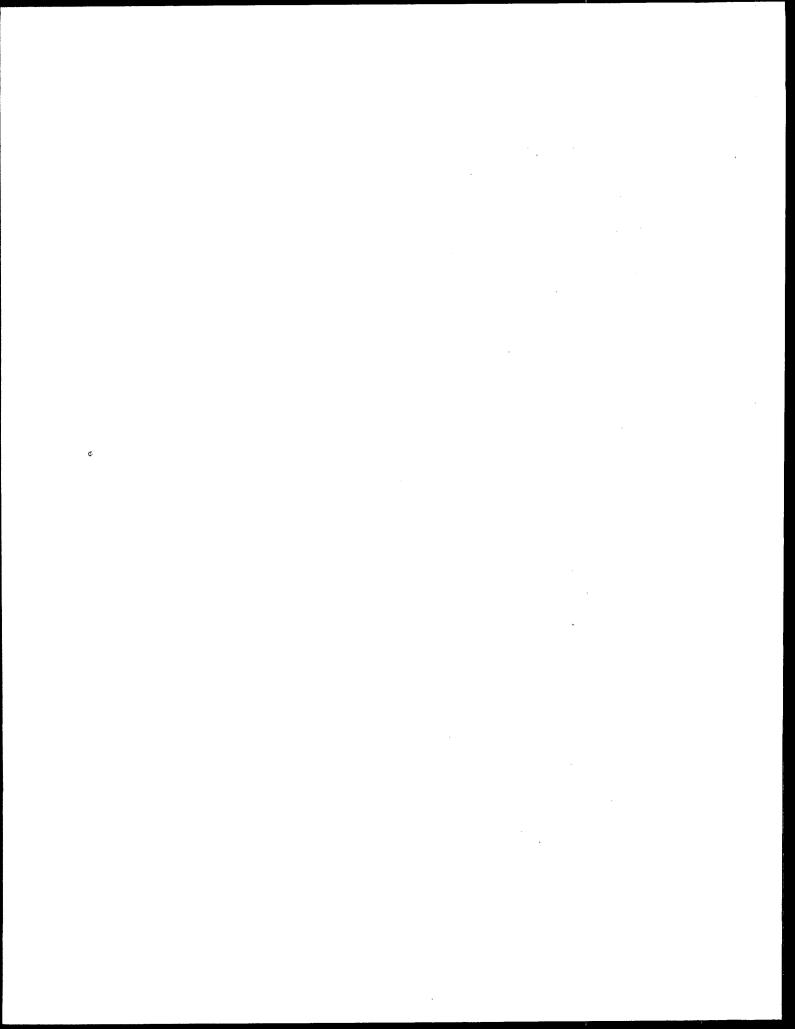

In sheer numbers, the vast majority of PWB manufacturers are small to medium enterprises with annual sales under \$10 million. The breakdown of the number of companies by size is shown in Table 1-2. These numerous smaller companies control only about 20% to 25% of the market dollar volume, while the largest 40 or so companies with annual sales over \$20 million control about 55% of the dollar volume of the PWB market. A breakdown of market share by size of company is shown in Figure 1-1.

The PWB industry directly employs approximately 75,000 people. Of this number, about 68% of employment is concentrated in production jobs—the highest ratio of production jobs for U.S. electronic manufacturing. Approximately 50% is the average for other electronic sectors. These employment figures do not include jobs generated by the related PWB material and equipment suppliers of the industry, nor the OEMs that produce PWBs for internal use.

| Annual Sales         | Number of<br>Companies | Average<br>Shipments per<br>Company | Total<br>Shipments |

|----------------------|------------------------|-------------------------------------|--------------------|

| Over \$50 Million    | 14                     | \$95                                | \$1,330            |

| \$20 to \$50 Million | 30                     | \$31                                | \$1,116            |

| \$10 to \$20 Million | 40                     | \$14                                | \$672              |

| \$5 to \$10 Million  | 85                     | \$7                                 | \$595              |

| Under \$5 Million    | 500 or more            | \$<1                                | \$349              |

| Totals               | Over 650               |                                     | \$4,062            |

Source: IPC Technology Marketing Research Council, June 1994.

Table 1-2. U.S. Independent PWB Manufacturers: Number and Size of Company by Sales (all dollars are in millions).

Figure 1-1. U.S. Independent PWB Manufacturers: Market Share by Size of Company. Source: IPC Technology Marketing Research Council, June 1994.

#### III. FINANCIAL ANALYSIS OF INDUSTRY

Printed wiring board manufacturing is a highly competitive global industry. Although PWBs are not a commodity item, many of the competitive pressures and sourcing patterns are typical of a commodity market.

#### A. Profitability

Profitability in the industry varies from year to year, but generally falls in the range from 0 to 3%. Extremely stiff foreign competition and adequate global capacity keep the profit range narrow. The net profit after taxes for the domestic PWB industry in 1992 was 1.6%, and in 1993 was 2.9%. While these trends vary annually, in general the largest companies outperform the smallest in terms of profitability, while the mid-size companies fluctuate more between extremes. The reasons for this trend are not entirely clear, but as PWB manufacturing becomes more expensive and capital-intensive, the largest companies may benefit from greater resources and economies of scale.

#### B. Operating and Financial Ratios

With respect to operating and financial ratios, the following is a summary of typical figures for the industry:

• Pre-tax return on assets: 3% to 5%

Net sales per employee: \$60,000 to \$110,000

#### IV. MARKET ANALYSIS OF INDUSTRY

#### A. World Market Summary

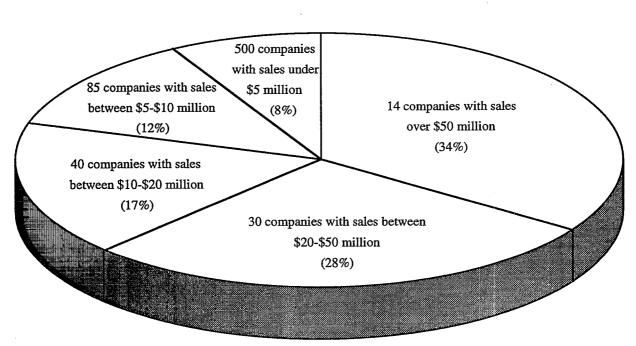

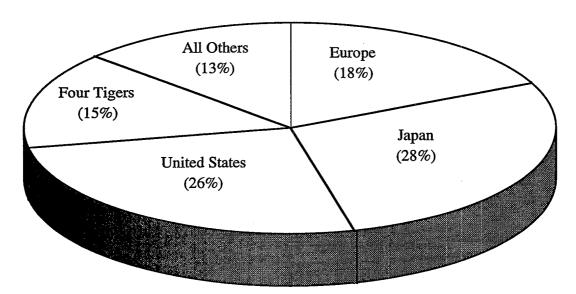

The total world market for all PWBs is approximately \$21 billion.<sup>1</sup> The United States and Japan are the dominant leaders, although the four tigers (Hong Kong, Singapore, Taiwan, and Korea) have been increasing market share in recent years. The distribution of production for rigid PWBs by selected countries and regions is shown in Figure 1-2. The breakdown of the world market for rigid PWBs by type of substrate is shown in Figure 1-3 and, as can be seen, multilayer boards dominate the world market.

A historical perspective on the world market share (in U.S. dollars) for PWBs is shown in Figure 1-4. U.S. domination of this world market eroded from 1980 to 1990, but has come back slightly in recent years. Japan and the four tigers have been the predominant competitors who have captured the world market share lost by the United States. Japan is now seeing its own market dominance erode as the four tigers continue to capture market share.

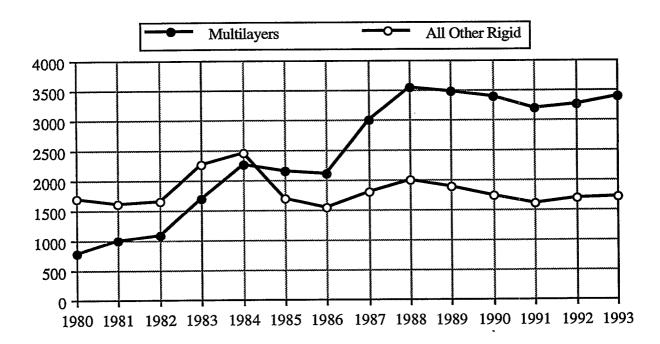

#### B. <u>Domestic Market History/Overview</u>

Since 1980, rigid multilayer PWBs have grown to dominate the domestic production value of all PWBs. Rigid multilayer boards now account for approximately 66% of the domestic market. One-quarter of the market is double-sided rigid boards, and the remainder are single-sided and flexible circuits. The market for multilayer boards has grown from approximately \$700 million in 1980, to almost \$3.4 billion in 1993. Figure 1-5 shows the history of this growth in the multilayer market.

Figure 1-2. U.S. Dollar Denominated<sup>1</sup> Share of World Rigid PWB Market for Selected Countries/Regions. Source: IPC Technology Marketing Research Council, June 1994.

<sup>1</sup> Exchange rates play a major factor in analyzing the world market. Growth and market share depend on which currency is used to measure the markets and the current exchange rate. All world market data in this report are measured in U.S. dollars based upon the exchange rate as of 31 December 1993.

Figure 1-3. U.S. Dollar Denominated¹ Production of World Rigid PWB Market by Type of Substrate.

Figure 1-4. Historical World Market Share for Rigid and Flexible Circuits (based on U.S. dollars).<sup>1</sup>

Figure 1-5. Comparison: Multilayers (including high-performance multilayers) vs. All Other Rigid PWBs (excluding flex). All Dollars in Millions. Source: IPC Technology Marketing Research Council, June 1994.

Although multilayer rigid boards dominate the dollar volume of production, single-sided PWBs by far dominate the number of circuit boards produced in the United States. Of the approximately 1.3 million PWBs produced in the United States in 1993, almost 900,000 were single-sided and only 150,000 were multilayer boards. However, the average cost for a single-sided board is 58¢, while the average cost for a multilayer board is about \$22 (Table 1-3).

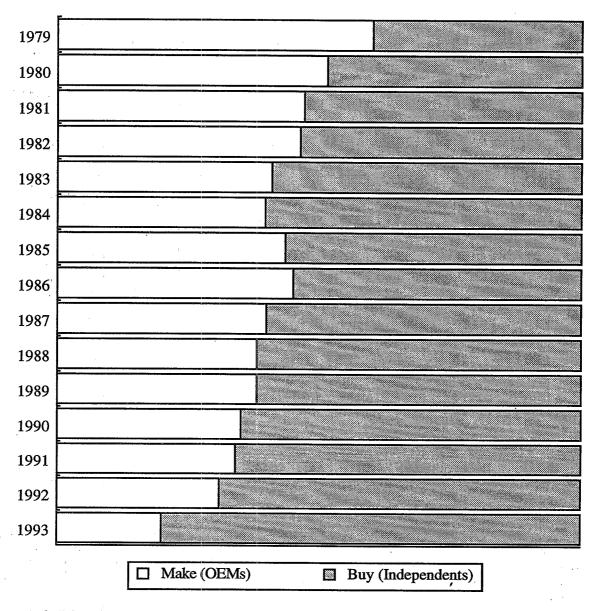

Another historical shift over the past ten years has been outsourcing PWB manufacturing. In 1980, captive OEM operations accounted for about 50% of the PWB market. Independent or merchant PWB manufacturers accounted for the other half. As is clear from Figure 1-6, captive houses have been shutting down their PWB manufacturing operations and instead purchasing PWBs from the smaller independent manufacturers.

| Type of PWB  | Total Value of<br>Production | Average Cost<br>per Board | No. of PWBs (in millions) |

|--------------|------------------------------|---------------------------|---------------------------|

| Multilayer   | \$3.350 billion              | \$21.74                   | 154,000                   |

| Double-sided | \$1.186 billion              | \$5.65                    | 210,000                   |

| Single-sided | \$0.521 billion              | \$0.58                    | 890,000                   |

| Totals       | \$5.057 billion              |                           | 1,254,000                 |

Source: IPC Technology Marketing Research Council, June 1994

Table 1-3. Quantity and Value of Domestic PWB Production.

Figure 1-6. Historic Trends of Make vs. Buy for PWB Production in the U.S. (by dollar volume). Source: IPC Technology Marketing Research Council, June 1994.

Now, only one quarter or less of the PWB manufacturing is done by captive houses. The remaining 75% to 80% is produced by independent PWB manufacturers. The reason for this shift is that OEMs are focusing on their core business—assembling the final consumer products—rather than manufacturing all the intermediate components such as PWBs or cathode ray tubes (CRTs). Thus, the OEMs now frequently purchase components (including PWBs, CRTs, subassemblies, drives, etc.) that can be readily out-sourced. Boards are purchased from independent PWB manufacturers who specialize only in PWB production, rather than try to maintain the hefty costs, expensive equipment, personnel, and technical expertise required for in-house PWB production. The introduction of computer-

aided design (CAD) has also facilitated the transfer of design information, and therefore, the outside manufacture of PWBs.

#### C. Imports/Exports

Import and export data on the PWB market is extremely difficult to estimate, primarily because the nomenclature and codes used by the International Trade Commission and the U.S. Department of Commerce are confused by printed wiring assembly and printed wiring board importers and exporters. Printed wiring assemblies are printed wiring boards on which electronic components such as integrated circuits, capacitors, and resistors have been mounted. With such valuable components mounted on them, the value of PWAs are clearly much greater than bare PWBs.

By combining the U.S. Department of Commerce data with their market research, the IPC estimates that domestic PWB imports are approximately \$500 to \$600 million annually. The largest single importer is Taiwan with about 30% to 35% of the import market. Japan, Hong Kong, Korea, and Thailand each have about 10% of the import market. With respect to exports, it is estimated that total domestic PWB exports amounted to about \$100 million dollars in 1993 (2% to 3% of total domestic production). This estimate does not include PWBs exported by OEMs in their equipment.

#### D. Major Domestic Markets and Trends

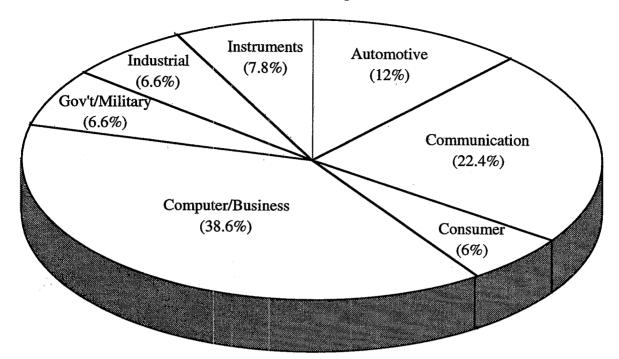

The seven basic markets for printed wiring boards are described below.

- Automotive: engine and drive performance, convenience and safety, entertainment (radios), and other applications for diagnostic display and security.

- Communication: mobile radio, touch tone, portable communication, pagers, data transmissions, microwave relay, telecommunications and telephone switching equipment, and navigation instruments.

- Consumer electronics: watches, clocks, portable calculators, musical instruments, electronic

games, large appliances, microwave ovens, pinball/arcade games, television, home entertainment, video records, and smoke and intrusion detection systems.

- Computer/business equipment: mainframe computers, mini computers, broad level processors, add-on memory, input/output devices, terminals, printers, copy machines, facsimile machines, word processors, cash registers, teaching machines, gas pumps, and taxi meters.

- Government/military/aerospace: radar, guidance and control systems, communication and navigation, electronic warfare, ground support, sonar ordinance, missiles, and satellite and related systems.

- Industrial electronics: machine and process control, production test and measurement, material handling, machining equipment, pollution, energy and safety equipment, numerical controls, power controls, sensors, and weighing equipment.

- Instrumentation: test and measurement equipment, medical instruments and medical testers, analytical, nuclear, lasers, scientific instruments, and implant devices.

A summary of the market share for these various groups is shown in Figure 1-7. By far the largest market is computers and business equipment, followed by communications and automotive. Automobiles will use increasing amounts of electronics, and communications demand will continue strong growth. Computer and business equipment may be leveling off, while government and military electronic demand is expected to remain weak in the face of Congressional budget cuts. Since the majority of consumer electronics products (e.g., TV, stereo, VCR) sold in the United States are produced

off-shore with off-shore PWBs, changes in the domestic consumer market will probably have little effect on domestic PWB production. These trends are expected to continue for at least the near future.

Figure 1-7. Market for PWBs in the United States in 1993. Source: IPC Technology Marketing Research Council, June 1994.

#### E. Analysis of Laminates and Process Consumables for Rigid Boards

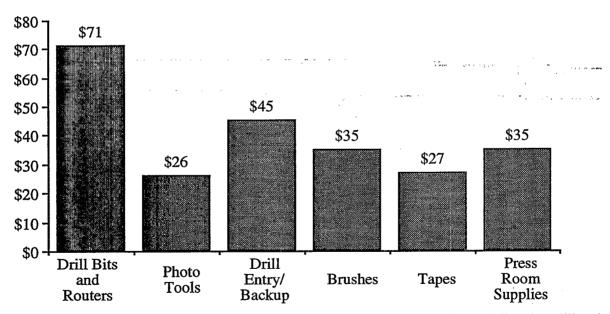

The printed wiring board product market is normally broken down in one of two ways: either by the type of substrate used (glass, paper, composite) or the type of board produced (single-sided, double-sided, multilayer). Table 1-4 shows the U.S. market summary for PWB production broken down by type of substrate used for rigid PWBs. Glass substrates compose the largest market segment by far. In addition to rigid PWBs, the United States also produces approximately \$400 million of flexible circuitry.

As part of the 236 million square feet of laminate used in 1993, the PWB industry consumed approximately 587 million square feet of copper foil and 52 million pounds of epoxy resin. The industry also consumed approximately 60 million pounds of fiberglass yarns used in 322 million square feet of pre-preg. Pre-preg is un-cured epoxy-fiberglass material used to separate and electrically insulate the layers of circuitry in a multilayer PWB. Figure 1-8 summarizes the sales of various process consumables in 1993, such as drill bits, brushes, and tapes. These process consumables exclude laminates as well as other chemicals. The value of chemicals used in the industry was approximately \$520 million. The primary chemicals used include the following:

- Plating chemistries (additive, electroless, electrolytic, etchback/desmear, oxide);

- Solder mask (dry film, photoimagible liquid, screen-defined);

- Etchants (ammoniacal, peroxide sulfuric, solder neutralizer);

- Imaging products (dry film, photoimagible liquid, screen defined, resist);

- Imaging chemicals (aqueous and insolvent developers and strippers); and

- Other chemicals (fluxes, metal strippers, cleaners, anti-tarnish, waste treatment chemistries).

| Type of Substrate     | PWB Dollar<br>Volume | Laminate FT <sup>2</sup> |

|-----------------------|----------------------|--------------------------|

| Glass, 1-sided        | \$110.2              | 6.03                     |

| Glass, 2-sided        | \$1,115.0            | 64.08                    |

| Glass, thin           | \$2,892.3            | 118.0                    |

| High-performance      | \$458.0              | 7.0                      |

| Paper, 1-sided        | \$8.0                | 1.0                      |

| Paper, 2-sided        | \$0.0                | 0.0                      |

| Composite, 1-sided    | \$425.2              | 38.0                     |

| Composite, 2-sided    | \$48.8               | 2.0                      |

| Totals for Rigid PWBs | \$5,057.6            | 236.0                    |

Source: IPC Technology Marketing Research Council, June 1994

Table 1-4. Domestic Rigid PWB and Laminate Production by Type of Substrate Used (all dollars in millions/all square feet in millions).

Figure 1-8. Sales of Various Process Consumables for Rigid Boards in 1993 (all dollars in millions). Source: IPC Technology Marketing Research Council, June 1994.

#### V. TECHNOLOGY TRENDS ANALYSIS OF INDUSTRY

PWB technology continually evolves—the major trends have focused on reducing the size and increasing the capacity of the PWB. These changes are often accomplished through advances in the following technologies: multilayer, surface mounting, fine-pitch, hole density, hole size, and multichip modules.

Using multilayer PWBs (especially high-layer count PWBs) increases capacity and reduces size by allowing more circuitry to be built into one PWB. Each layer has its own circuit pattern. Similarly, using surface-mount technology allows components to be placed on both sides of the PWB instead of just one side, as is the case with through-hole technology. With through-hole mounting, the pins or leads on the component are inserted through holes in the PWB and come out the other side, thereby using up space on that side of the PWB. With surface-mounted components, the pins or leads are attached to pads or lands on one surface of the PWB, so the opposite side of the PWB remains free for either other components or circuitry. A pad or land is the end of a circuit line or trace intended as the connection point for a component. Typically, the pad or land is significantly wider than the rest of the circuit trace in order to approximately match the width of the component lead that will be attached to it.

Pitch refers to the distance from a point on a particular feature to the same point on the adjacent feature. Pitch, as used by the PWB industry, frequently defines the distance from the center of a circuit line (also called "trace") to the center of the adjacent line. The thinner the line and space (or finer the pitch), the more lines can be placed on the PWB. Similarly, density refers to the percentage of the PWB covered by conductors or by components. To save routing space with large-pitch components, PWB designers run circuit lines in-between adjacent pads on which the component leads are mounted. High-density PWBs may have three or more conductors between the pads.

Another technique to reduce size and boost performance is to decrease the size of the vias or holes used to conduct electricity from one side of the PWB to the other or to an inner layer. Finally, another technology for increasing performance while decreasing size is multichip modules (MCMs). For most applications, the bare integrated circuit (IC) chip is sealed in a hermetic or plastic package before being mounted on the PWB. This package protects the IC from moisture and other hazards, but takes up space and increases weight. MCMs consist of multiple bare IC chips mounted directly on a substrate, often quite similar to a small PWB. This MCM can then be coated for protection and used as is as a special type of PWB or mounted on another PWB as part of a larger PWA.

#### A. Multilayer Technology

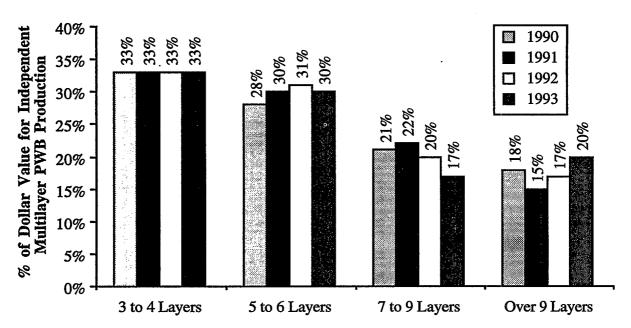

The following information on trends in multilayer technology, as shown in Figure 1-9, refers to the number of different layers used as a percent of all multilayer boards sold. Multilayer PWBs account for about 66% of the market, as discussed in Section IV.B. As evident from Figure 1-9, the relative distribution of three- to four-layer boards has been relatively steady for several years, while that of multilayer boards with nine or more layers has risen slightly over the past three years. In general, however, the production of two- to four-layer boards has declined over the past ten years from approximately 48% of the market in 1984 to 33% of the market in 1993. That decline has been matched by a rise in production of nine plus multilayer boards. The largest markets for multilayer PWBs are computers and communications where size and performance are critical. Consumer products use many single-sided PWBs because cost is paramount, while size and weight are less critical. For this same reason, the market uses many 1- and 2-sided PWBs.

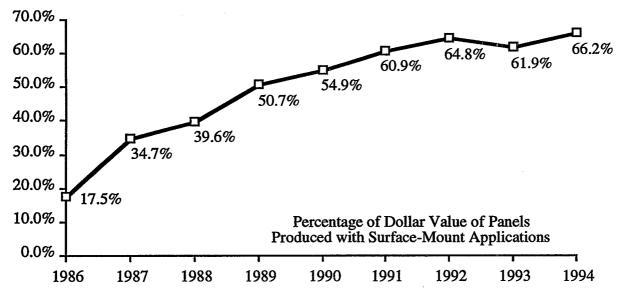

#### B. Surface Mount

Surface-mount applications (as opposed to through-hole components) save space and allow increased component density on the printed wiring assembly. A history of the growth of surface-mount applications for independent PWB manufacturers is shown in Figure 1-10. In addition to rising surface-mount applications, the percentage of boards with surface-mount applications on both sides of

Figure 1-9. Historical Trends for Layer Count in Multilayer PWBs. Source: IPC Technology Marketing Research Council, June 1994.

Figure 1-10. Historical Trends on Surface Mount Applications in PWB Production. Source: IPC Technology Marketing Research Council, June 1994.

the boards has also been increasing steadily for at least the past seven years, which allows increased performance and decreased size. Of the percentage of all panels with surface-mount applications, the fraction with surface-mount applications on both sides of the panel has increased from about 6% in 1987 to around 21% in 1994. In addition, the percentage of PWBs with 100% surface-mount patterns (i.e., no through-hole components) has increased from about 4% of all panels in 1988 to around 10% of all panels in 1994.

#### C. Fine-Pitch

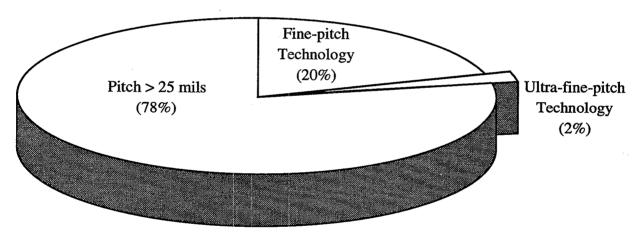

Fine-pitch technology is generally defined as boards with 15 to 25 mils (thousandths of an inch) applications. If the pitch is over 25 mils, the PWB is not a fine-pitch PWB. Ultra-fine-pitch applications generally refer to applications under 15 mils. The use of fine-pitch technology generally can be traced two ways: historically, and by type of PWB manufacturer (OEM vs. independent). With reference to the former, fine-pitch and ultra-fine-pitch applications have been increasing steadily since the industry began collecting data in 1989. Now, approximately 20% of all PWBs produced have fine-pitch applications, and 45% of surface-mount PWBs have fine-pitch applications. This is approximately double the percentages of five years ago. In addition, ultra-fine-pitch technology is used in about 2% all boards and 4% of surface-mount boards (Figure 1-11). Two factors drive increasing fine- and ultra-fine-pitch technology: the demand for higher performance with reduced size, and increasing technological capabilities that allow fine-pitch PWBs to be produced more reliably.

Figure 1-11. Use of Fine-pitch Technology.

#### D. Density and Hole Sizes

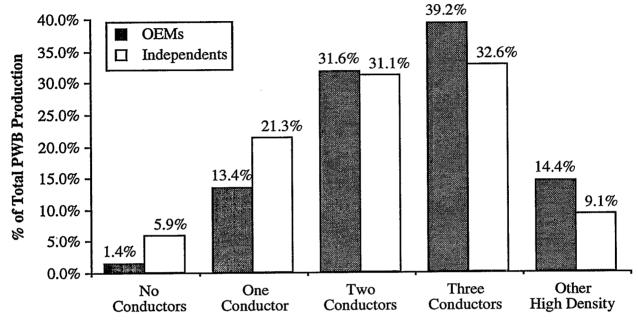

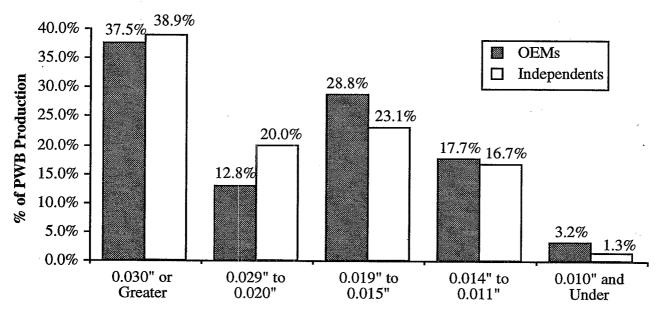

For this report, the criteria used to measure density applications is the volume of PWB production with a certain number of conductors between lands on 100-mil (0.100") centers (center refers to the center of the land). Density, in this instance, refers to the number of conductors between lands. Thus, a board with no conductors between 100-mil lands is very low density. The data on density production in 1993 is shown in Figure 1-12.

The majority of PWBs produced are medium to high density, with two or three conductors, respectively, between lands. As is often the case, demand for higher performance and smaller size drive higher densities, while cost constraints drive lower densities. High-density PWBs are usually more ex-

pensive to produce because of the yields and the greater level of testing that is required (e.g., optical testing of inner layers prior to lamination). The historical trend for density can be summarized as follows: low-density applications (0 to 1 conductors between 100 mil centers) have been steadily declining for approximately 10 years, medium-density boards (2 conductors between 100 mil centers) have remained steady at around 26% to 32%, and high-density applications (3 or more conductors between 100 mil centers) have been steadily increasing over the same time. Thus, the performance/size demands are slowly winning over the cost constraints. At the same time, the technology for producing high-density PWBs has been improving.

Figure 1-12. Density of PWB Production Based on Dollar Value of Production: OEM vs. Independents. Source: IPC Technology Marketing Research Council, June 1994.

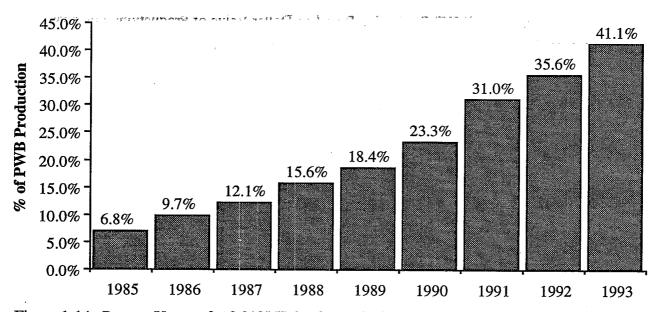

With respect to hole sizes, an overview of percent of production for various hole sizes in 1993 based on dollar value of production is shown in Figure 1-13. In general, use of smaller holes (0.019" or less) has been steadily increasing over the past 10 years from approximately 7% in 1985 to over 40% in 1993 (Figure 1-14). Once again, smaller holes are generally more difficult and expensive to produce, but they do save space.

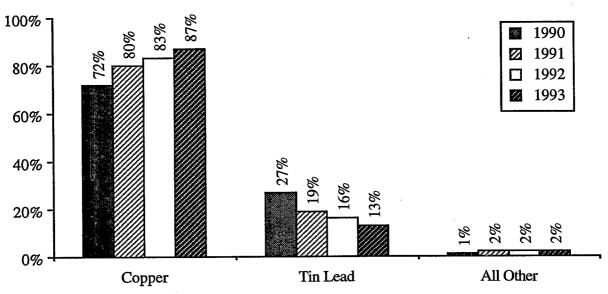

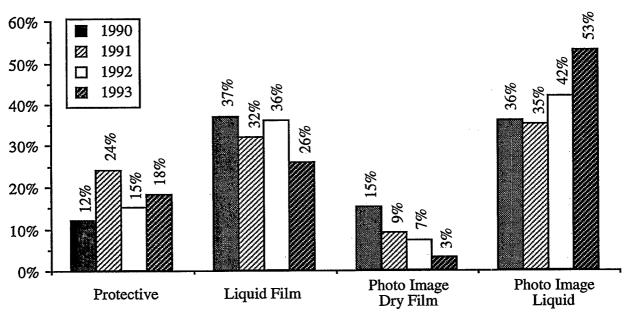

#### E. Plating and Coating

Platings and coatings on PWBs are primarily used during fabrication for the following purposes: as an etch-resist (typically tin-lead plating); to ensure solderability, typically tin-lead plating or flowed-on solder through HASL (Hot Air Solder Leveling); to protect against moisture or oxidation (often a conformal coating or solder mask); or to mask (cover) certain parts of the PWB against being plated with solder (solder mask). Following are two historical charts on the various types of surface finish and plating or coating techniques used by the PWB industry for the past four years (Figures 1-15 and 1-16).

The use of liquid film solder mask and photoimagible dry film solder mask has been generally declining, while the use of photoimagible liquid solder mask has been generally increasing. In addition, for the past four years, the industry has been trying to reduce lead consumption by eliminating tin-lead plating on boards, substituting instead tin plating or organic coatings.

Figure 1-13. Percent of Production for Various Hole Sizes Based on Dollar Value of Production for 1993. Source: IPC Technology Marketing Research Council, June 1994.

Figure 1-14. Percent Usage of ≤ 0.019" Holes from 1985 through 1993 Based on Dollar Value of Production. Source: IPC Technology Marketing Research Council Technology Trends Report, 1993.

Figure 1-15. Historical Trends in PWB Surface Finish Techniques Based on Dollar Value of Production. Source: IPC, Technology Marketing Research Council, June 1994.

Figure 1-16. Historical Trends in PWB Protective Coating Techniques. Source: IPC Technology Marketing Research Council, June 1994.

### F. Multichip Modules

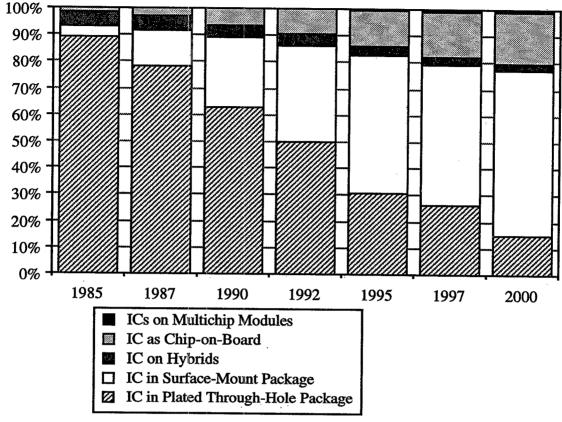

The traditional and still most widely used methods for packaging ICs or "chips" are either surface-mount packages or plated through-hole (PTH) packages. However, in recent years new packaging/assembly methods have been developed, including bare chip attachment methods such as chip-

on-board (COB) and MCMs. Although MCMs are still not widely used, this packaging/assembly method is expected to increase in the near future as shown in Figure 1-17.

Figure 1-17. Worldwide IC Packaging Methods.

The advantages of multichip modules include the following:

- Interconnect a variety of bare, high-pin-count chips;

- Substantially reduce substrate area and signal delays;

- Reduce second level interconnection density;

- Improve electrical performance and heat extraction;

- Reduce system costs and design time;

- Mix digital, analog, and optical chips; and

- Incorporate discreet components in the substrate.

The three basic MCM types are defined by the type of substrate used and are as follows:

- Ceramic multichip modules (MCM-C), which use ceramic materials as a substrate;

- Deposited dielectric multichip modules (MCM-D), which use deposited dielectric films and metal conductors, similar to integrated circuit technology; and

- Laminate multichip modules (MCM-L), which use existing PWB materials, technologies, and facilities. MCM-L assemblies are smaller PWBs with a high packaging density and fine lines and spaces of interconnect.

# PART TWO: PRINTED WIRING BOARD USE CLUSTER PROFILE

#### I. OVERVIEW

#### A. Introduction

Printed wiring boards (PWBs) form the basis for interconnecting the devices and components in the vast majority of electronic products. Without this critical component, most electronics products could not function or would be significantly more expensive if constructed with other interconnect technologies. This use-cluster profile will describe the PWB fabrication process for the largest product segment of the industry, the rigid multilayer PWB. The profile focuses on the "subtractive" process, as it is the only broadly implemented approach to fabricating PWBs. Fully "additive" approaches are under development, which would radically change the overall process flow and are described briefly in the Sections I.C.5 and I.C.6.

#### B. Use Cluster Profile

A use cluster is a set of chemicals, processes, and technologies that can substitute for one another to perform a specific function. A use cluster profile of the PWB industry, therefore, describes alternate chemicals, processes, and technologies that may be used to complete each step or function in the entire PWB manufacturing process.

This use cluster profile is intended to aid in the selection of a use cluster for assessment in a Design for the Environment (DfE) project. The profile identifies different processes in the PWB industry (e.g., laminating, making holes conductive) and steps within those processes (e.g., imaging, etching, plating). The process steps are described in flow chart form with a description of each step. Next, the chemicals, materials, and technologies used in each step are briefly described. The profile may also mention commonly accepted alternatives to these practices, and processes or materials that are recognized to have especially high environmental impacts. Information on the risk and releases of these materials can then be used to target areas for further work.

## C. Overview of PWB Types and Manufacturing Methods

Printed wiring boards are categorized in several ways. When overall complexity is being considered, they are often categorized in terms of layer-counts, or the number of circuit layers present on a single PWB. PWBs are usually broken down along layer-count lines into three categories: multi-layer, double-sided, and single-sided. Multilayer PWBs contain more than two layers of circuitry, i.e., at least one layer is imbedded in the substrate beneath the surface of the board. A multilayer board may consist of 20 or more interconnected layers, but more common are 4, 6, and 8 layers. Double-sided boards have two interconnected layers and are generally easier to produce than multilayer PWBs, while single-sided PWBs have only one layer of circuitry.

PWBs are also categorized by substrate, or base material, type and fall into three basic categories. Rigid PWBs typically are constructed with glass-reinforced epoxy-resin systems that produce a rigid board at thicknesses of less than 0.1" (0.062" is the most common rigid PWB thickness, although there is a trend toward thinner PWBs). Flexible (or flex) circuits are manufactured on polyimide and polyester substrates that remain flexible at finished thicknesses—ribbon cables are common flexible circuits. A third category of PWBs consist of boards that are essentially combinations or assemblies of the first two: rigid-flex combinations of one or more rigid PWBs that have one or more flexible circuits laminated to them during the manufacturing process. Three-dimensional circuit assemblies can be created with rigid-flex combinations.

Manufacturing methods can be boiled down to two types, although hybrid methods exist. Most common is subtractive processing, in which copper is selectively removed from a PWB to form a circuit. Within this process, however, copper and other metals are also added during plating steps. The term "subtractive" refers to the method of image transfer from a photo-tool or image file to a copper circuit on a PWB. Additive processing refers to a process in which an image is formed by selectively adding copper (electrolessly plating onto a substrate an image of a circuit). In a fully additive process no etching, or removal of copper, occurs.

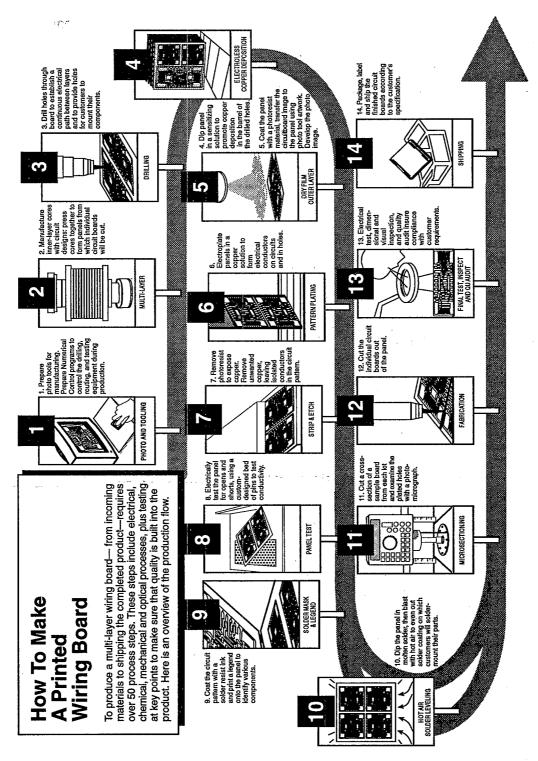

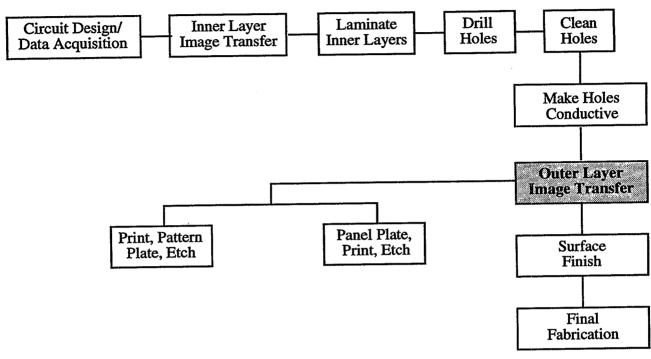

As part of an industry driven activity, the 1994 Electronics Industry Environmental Roadmap<sup>2</sup> described a generic PWB process, developed in conjunction with the IPC, with comments from technical experts participating in the process (Figure 2-1). Representative of the highest value segment of the PWB market, this process flow is indicative of the manufacture of rigid multilayers. This process description was used as a baseline for selection and definition of the use clusters in this analysis.

### 1. Single-sided Manufacturing Overview

Single-sided PWBs continue to be manufactured in high quantities in term of units (71% of PWBs manufactured in the U.S.), but represent only 10% of the total value of U.S. production. Single-sided PWBs are comparatively easy to produce and the market is highly competitive, as demonstrated by the fact that a single-sided PWB costs only about one-tenth that of a double-sided PWB.

Several critical manufacturing steps are not included in the typical single-sided manufacturing sequence and no process is unique to single-sided production. Therefore, any manufacturer of double-sided or multilayer PWBs can produce single-sided ones as well. Few shops produce single-sided panels exclusively, but instead include single-sided PWBs as part of their overall product mix. Many shops do not produce single-sided panels at all due to the market conditions mentioned above.

The most common sequence of single-sided production is drill, print-and-etch, surface finish, and final fabrication. No inner-layer processing is required, and desmear is also eliminated. Furthermore, only in rare cases are plated through-holes required, therefore, the entire cluster of making holes conductive is not applicable to single-sided manufacturers. The holes instead provide mechanical stability for through-hole panels. Drilling may be completely eliminated on single-sided PWBs if the components are all surface-mounted. Alternative methods of single-sided manufacturing are available. For example, for prototyping, single-sided PWBs can be created by selectively milling or routing copper with an NC machine, thereby forming a circuit without using wet processes at all. Other table-top prototype systems have also been devised.

## 2. <u>Double-sided Manufacturing Overview</u>

Not unlike single-sided, double-sided PWB manufacturing is also a subset of the multilayer process described in Section II. The inner layer image transfer, lamination, and hole cleaning clusters are not performed. Therefore, any multilayer manufacturer can easily produce double-sided panels and most do so. Double-sided PWBs do require electroless copper or other methods of making holes conductive, since the top and bottom sides of the board require interconnection.

<sup>2</sup> Pedersen, Pitts, et al., Electronics Industry Environmental Roadmap, MCC, 1994, p. 39.

Figure 2-1. The Basic Manufacturing Flow for the Fabrication of Rigid Multilayer PWBs.<sup>3</sup>

<sup>3</sup> Pedersen, Pitts, et al., Electronics Industry Environmental Roadmap, MCC, 1994, p. 39.

### 3. Multilayer Manufacturing Overview

Single- and double-sided manufacturing processes are subsets of the multilayer process. Thus, it is logical to use the multilayer process as the focus of this profile. In addition, multilayer boards represent two-thirds of the overall value of U.S. production dollars, even though they are produced in lower numbers than single- or double-sided PWBs. The rigid multilayer process (rigid PWBs represent about 95% of U.S. production) is discussed in detail in Section II.

### 4. Flexible PWB Manufacturing Overview

A flexible circuit is manufactured on materials that allow for the bending or flexing of the PWB to create a three-dimensional effect. Flex circuits may be designed to be bent into shape once or a few times, or to withstand thousands of flexing cycles. They are found in printers, disk drives, automobile electronics, and a wide range of other common products.

Although similar to rigid manufacturing in many respects, the flexible circuit manufacturing process deals with unique materials and surface finishes, and the process is not integrated into a rigid PWB shop without considerable effort. Therefore, few rigid manufacturers have expanded into the flex market. On the other hand, because an important portion of the flex market is rigid-flex combinations or assemblies, manufacturers of predominantly flex substrates often produce rigid boards as well. Because flexible substrates have larger dimensional tolerances than rigid ones, multilayer flexible circuits are more difficult to manufacture and are less common than rigid multilayer PWBs.

Image transfer, drilling, and through-hole plating are performed in a similar, but not identical manner. Flex substrates are thin and are unlike standard rigid materials—some common flex materials are polyimide and polyester, although many others are in use. Thicknesses of only a few mils are common compared with inner-layer rigid material thicknesses of up to 31 mils, and double-sided thicknesses of 62 or more mils. Additionally, tooling and surface finish processes for flexible circuits are quite different from those of rigid PWBs. A cover sheet of similar material to the base film is applied over typical flex circuitry rather than a solder mask and is press laminated over the circuitry. The cover sheet is pre-punched to expose appropriate areas of the circuit for soldering of components and connectors. Not all flex circuits require solder; those that do are hot-air or hot-oil solder-coated. Nickel-gold is also a common finish.

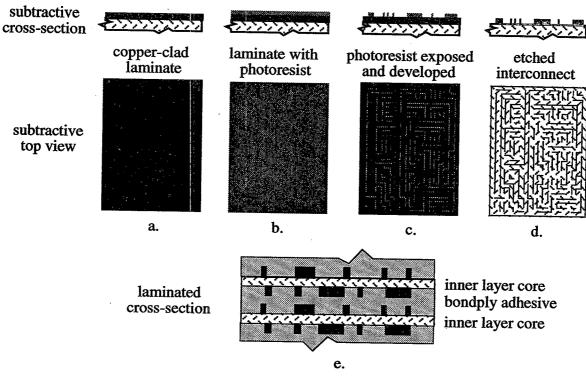

#### 5. Subtractive Overview

The fabrication of PWBs through the years has relied mainly on a subtractive print and etch process for forming copper conductors. The process flow shown in Figure 2-1 describes such a subtractive approach. In a subtractive process for rigid multilayer PWBs, metal is removed from a solid foil to form the desired interconnect pattern for the inner layers, as shown in Figure 2-2 and described below. The label subtractive comes from the typical processes used for making these inner layers, encompassed in step 2 of the overall process shown in Figure 2-1.

As shown in Figure 2-2, the subtractive process begins with copper-clad laminate, composed of a thin copper foil covering both sides of the epoxy-glass core material (a). The laminate is coated with a sacrificial photopolymer material that acts as a resist in subsequent steps (b). The resist is photoimaged (exposed/developed) to expose the copper to be removed (c). The board is then etched, after which the resist material is stripped and disposed in a fabrication waste stream, leaving the desired interconnect pattern in copper on the exposed laminate (d). In a multilayer structure, each of the inner layers is constructed independently, then laminated together using a B-stage epoxy in between each inner layer core

to form the overall structure (e). This non-sequential process of building multilayers is essentially independent of the number of inner layers laminated together and is used to build PWB structures with any number of layers.

Figure 2-2. The Simplified Subtractive Process for Manufacturing Inner Layers of Rigid Multilayers (a through d), and a Cross-Section of Two Inner-Layer Cores within a Multilayer Structure (e).

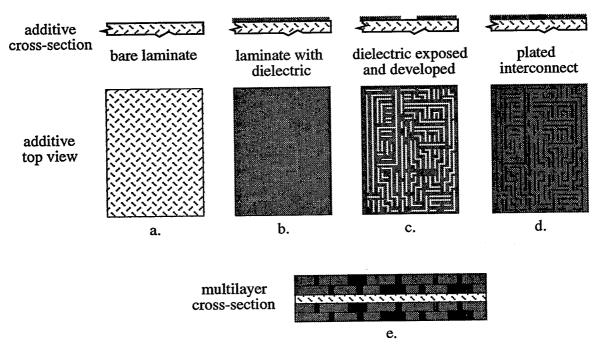

### 6. Additive Overview

Full-build additive approaches for double-and single-sided boards have been in use for over 20 years. Processes that use full build to make multilayer boards have only recently been under development in this country, and none are in widespread use. Since the additive deposition of seed layers is used for electroplating at certain steps within a subtractive process flow, the full-build descriptor is intended to describe a process where the metal deposition is fully additive, eliminating all etching steps. The intent of these novel approaches is to take advantage of the PWB industry's current capabilities in photoimaging and printing as used in subtractive processes, while overcoming the limitations and expense of plating, etching, and lamination, as well as eliminating the drilling of vias to form the vertical interconnect between layers.

Each layer is built upon the previous one, so this type of additive approach is also known as a sequential build. As such, there is no lamination step required. Yield considerations become more critical in sequential processing, because an irreparable flaw in the final layer destroys the entire structure. In subtractive processing, the inner layers can be inspected prior to lamination to ensure a higher overall yield.

As shown in Figure 2-3, the additive process for rigid boards begins with a bare catalyzed laminate with no metal on the surfaces (a). Alternatively, with some processes, the first layers on either side of the core laminate are etched to form power and ground planes and may already have plated through-holes. The laminate is coated with a permanent photodielectric material that acts as the dielectric separating the metal layers (b), thus replacing the subsequent core and B-stage layers in the subtractive approach. The dielectric is imaged and developed to form the vias, then a second layer is applied to form the interconnect pattern (c). The board is then selectively plated or metallized by other means, forming the desired interconnect pattern (d). In a multilayer structure, steps (b), (c), and (d) are repeated to form the overall structure (e). In contrast to the conventional subtractive process described previously, this process requires no lamination, with the unreinforced layers built sequentially on the initial rigid core.

Figure 2-3. The Simplified Full-Build Additive Process for Manufacturing Inner Layers of Rigid Multilayers (a through d), and a Cross-Section of a Multilayer Structure (e).

## 7. Additive Metallization Techniques

Several methods are under consideration for deposition of the circuit traces and vias in an additive structure. None of these methods have been broadly commercialized due to either the maturity, the economics, or outstanding technical challenges. Current research is addressing all of these issues.

## a. Solid Systems